#### University for Business and Technology in Kosovo

### **UBT Knowledge Center**

**UBT International Conference**

2016 UBT International Conference

Oct 28th, 9:00 AM - Oct 30th, 5:00 PM

### Circuit Design for Green Communications - Methods, Tools and **Examples**

Galia Marinova Technical University Sofia, gim@tu-sofia.bg

Zdravka Tchobanova Technical University Sofia, z.chobanova@tu-sofia.bg

Follow this and additional works at: https://knowledgecenter.ubt-uni.net/conference

Part of the Communication Commons, and the Computer Sciences Commons

#### **Recommended Citation**

Marinova, Galia and Tchobanova, Zdravka, "Circuit Design for Green Communications - Methods, Tools and Examples" (2016). UBT International Conference. 51.

https://knowledgecenter.ubt-uni.net/conference/2016/all-events/51

This Event is brought to you for free and open access by the Publication and Journals at UBT Knowledge Center. It has been accepted for inclusion in UBT International Conference by an authorized administrator of UBT Knowledge Center. For more information, please contact knowledge.center@ubt-uni.net.

#### Circuit Design for Green Communications – Methods, Tools and Examples

Galia Marinova<sup>1</sup>, Zdravka Tchobanova<sup>1</sup>

<sup>1</sup>Technical University-Sofia, Faculty of Telecommunications, 8, bul. "Kliment Ohridski", Sofia-1000, Bulgaria {gim, z.chobanova}@tu-sofia.bg

Abstract. The paper makes an overview of the existing methods applied for circuit design with low power consumption objective. It considers Computer-Aided Design (CAD) tools and modules for power consumption estimation at the design stage. For analog and mixed analog-digital circuit design, the power estimation options in ORCAD Design Suit with PSpice and Analog Filter Wizard are studied. For digital communication systems the study covers the power estimation, analysis and optimization in ISE and Vivado systems, Xilinx Power Estimator (XPE) tool and spreadsheet, the XPower Analyzer, as well as similar tools proposed by ALTERA - PowerPlay Early Power Estimator and QUARTUS II Power Play Power Analyzer. Two examples are developed: Power consumption estimation of a Universal Software Radio Peripheral (USRP)-based communication system design, based on datasheets and software energy monitoring tools, and power consumption estimation of a Kasami pseudo-random sequence generator circuit design on FPGA using Vivado.

**Keywords**: Low Power Consumption, CAD tools, Power Estimation, FPGA, USRP, Analog and Analog-Digital Circuits

#### 1. Introduction

Low power consumption is an important objective in green communications, which has to be taken in consideration as early as possible at the design stage. It's also a criterion for the selection of solution and technology for a given application. The paper considers methods and tools that can help circuit designers to develop green design for communications. The outline of the paper is: First an overview is made of the methods for power estimation and low power design in communications, then tools for power estimation in CAD systems and Software energy monitoring tools are studied with application for analog, analog/digital and digital circuits on FPGA and USRP platforms; Two examples of power estimation for design on FPGA and USRP-based design are developed to illustrate the application of different tools for power estimation; At the end there concluding remarks and plans for future research are given.

## 2. Methods for Power Estimation and Low Power Circuit Design in Communications - state-of the art

Here are noted low power design solutions for different hardware realizations, proposed in scientific literature. Methods and approaches provided in literature are based on temperature

estimation and relocation of processing elements from hot spots to cool spots on FPGA, switching between different radio standards, parametrization and Dynamic and partial reconfiguration of FPGA, VHDL and Verilog coding for low power consumption and development of domain specific reconfigurable processor.

Authors in [1] start with the definition of total power consumption in an FPGA as:

$$Pt = Pst + Psc + Pdy, (1)$$

where Pt is total power, Pst is static power, Psc is short-circuit power and Pdy is dynamic power, the predominance being of dynamic power. The authors propose to measure local temperature in the chip by sensor system (array of temperature sensors embedded in the FPGA) which measures the temperature at different locations on the FPGA and high temperature spots are identified. The method is illustrated on Virtex-5 FPGA with ML550 board (Xilinx). Autors demonstrate that power consumption can be decreased through moving processing elements from hot spots at low temperature spots and through design area reduction.

In paper [2] the authors compare 3 methods of hardware realization of elements in software defined radio – Velctro approach (based on switching between different radio standards using a multiplexor), Parametrization approach (including parametric tuning of any function) and FPGA Dynamic and Partial Reconfiguration (DPR), where part of the system is reprogramed while the rest of the system is running. The comparison is estimated for a convolutional coder circuit with r=1/2 and K=3 and DPR approach is pointed as giving the lowest power consumption of the design.

The authors of paper [3] describe the design of a 4-bit asynchronous counter, developed in Xilinx ISE 14.2 and implemented on Virtex-6 FPGA, XC6VLX250T with ML605 development board. The power consumption is estimated through XPower 14.2. Two types of coding are compared – mapping the *clock enable* to the control port (Verilog and VHDL codes are proposed) and to the LUTs. The second design gives a lower power consumption estimate and the reduction obtained is 6%. This is due to the different number of LUTs, D flip-flops, clock buffers and IO buffers, the power consumption being proportional to the number of elements used for the realization of the HDL on the FPGA.

Paper [4] is focused on the implementation of cryptographic algorithms with public key. A domain-specific reconfigurable cryptographic processor (DSRCP) is developed. The analysis shows that only 5% of the total power is used for useful processing and 65% is dissipated in the programmable connection. DSRCP is 2 to 3 times more energy effective than the software solutions or FPGA solutions, Xilinx XC4000 is used for comparison. Some basic instructions for low power VLSI chip design are proposed in [15].

# 3. Tools for Power Estimation in CAD Systems and Software Energy Monitoring Tools

There are several papers on green communications emphasizing on their importance and concluding with advices for appropriate policies. A study on tools for power estimation is performed to help low power design and optimization.

### 3.1. Power Estimation and Optimization in CAD Systems for Analog and Analog-Digital Design

An estimation of power dissipation in analog and analog-digital circuit designs can be obtained in Cadence ORCAD/PSpice simulator [6] through the *Operating point analysis* and the results are listed in the output file as Total power dissipation in Watts.

Total quiescient power 120uA x 10V = 1.2mW

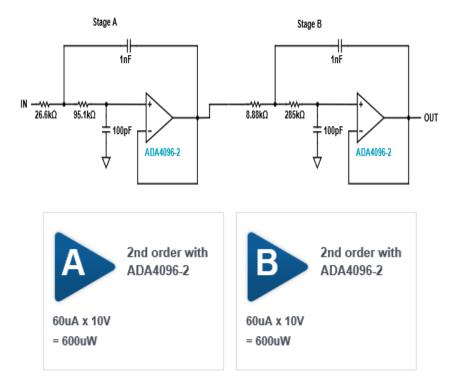

Fig.1. Low pass filter realization in Analog Filter Wizard tool and results from power estimation in the tool

Other analog design tool that provides power estimation options is Analog Filter Wizard of Analog Device [7]. Figure 1 illustrates Low pass filter realization in Analog Filter Wizard tool and results from power estimation in the tool. The quiescent power consumption of the filter is calculated. The input signal which can have a significant impact on power consumption is not modeled. The tool offers an option for Low power optimization, as well. The quiescent power consumption of the example from Fig.1 is 1.2mW.

### 3.2. Tools for Power Estimation and Analysis in FPGA-Based Digital Circuit Design

The serious focus of circuit designers on green communications design and more specifically on low power design has influenced FPGA providers, as Xilinx, to develop Power efficiency and management strategies and to consider e FPGA Performance-Per-Watt Metric for new low power device families. The main estimates on FPGA are based on Worst-Case Power Analysis. The impact of the implementation of different FPGA families for a single design can be studied using Xilinx Power Estimator (XPE) tool [13]. Thermal analysis, system packaging and need of heatsinks, which are closely connected to power consumption analysis, are also considered.

FPGA providers propose two kind pf tools for low power design – the power estimators and the power analyzers which are options in the development tools. The principal features and of these tools are given further.

Xilinx Power Estimator (XPE) is an Excel based online tool offered by Xilinx for early determination of power and cooling specifications in FPGA designs. It's based on Worst case power analysis and it's integrated with ISE and Vivado suits. Calculators are provides for different device families (UltraScale<sup>+TM</sup>, UltraScale<sup>+TM</sup>, 7 Series and Zynq-7000, Virtex-5 and Virtex-6, Spartan-3A/3AN/3A DSP and Spartan-6, Spartan-3E, Spartan-3, Virtex-4). Family, device and package are selected for a given project, environment parameters are defined and a Summary of *Total-On chip power, Junction Temperature, Thermal margin* and *Effective θJA* are calculated, graphs of *On-chip power per function, On-chip typical versus Maximal power, On-chip power over Vccint, On-Chip power over Junction temperature* and *Static current by supply* are drawn. Xilinx power analyzer is an option in both ISE and VIVADO tools. The On-chip power is calculated with confidence level. Both ISE and VIVADO propose similar estimations. In VIVADO an additional graphical presentation is added.

PowerPlay Early Power Estimators (EPE) and QUARTUS Prime PowerPlay Power Analyzer are the tools provided by ALTERA [14] for power consumption estimation of designs on ALTERA FPGAs. EXCEL based estimators accompanied with user guides for different ALTERA device families (Statix, Cyclone, Arria, MAX) are downloadable. Besides the input data for the family, device, package and environmental parameters, a selection of power regulator is proposed. Static and total power, are calculated, as well as power per function. No graphs are available.

#### 3.3. Software Energy Monitoring Tools

Software energy monitoring tools are used for estimating the real power consumption. They give information about the load of computer components in percent or the energy consumption by different components.

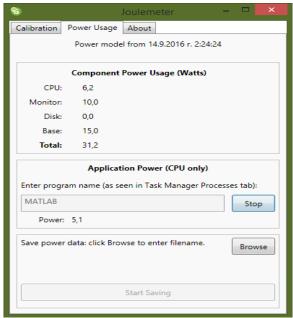

Microsoft Joulemeter [9] is such a tool in Windows OS and it gives information about the power consumption by different components and applications. When such a tool is run the changes in power consumption can be followed in real time in the panel Component Power Usage (Watts), where a running application or software program to be followed can be selected. Its name is written in the Application Power panel (CPU only). Bellow its power consumption is given as shown on Fig.2. This information can be saved in a file.

Fig.2. MS Joulemeter screen

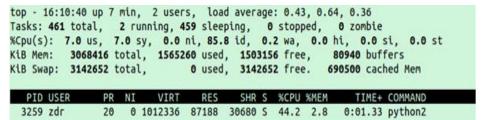

In Linux OS similar tool can be started from the terminal. For example the command *top* gives an information for: process ID (PID), effective user name of process owner(USER), priority (PR), the percentage of the CPU (% CPU) and the memory (% MEM), the accumulated CPU time (TIME +), the name of the executable file (COMMAND) as shown on Fig.3.

Fig.3. Information generated by the command top in Linux OS

## 4. Examples of Power Estimation in Communication Circuit Design

Two examples are developed and presented to illustrate the application of different tools for power estimation of designs implemented on FPGA and USRP platforms.

### 4.1. Estimation of the power consumption of a Kasami random bit generator circuit

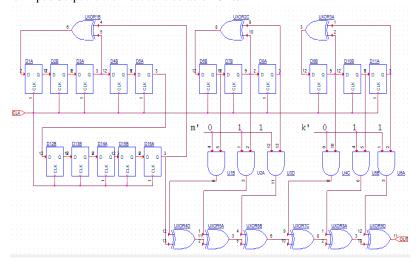

The circuit studied is Kasami pseudo-random sequence generator [5] defined by the polynomial of degree 10:

$$f(x) = x^{10} + x^3 + 1 \tag{2}$$

with m' = 011 and k' = 011.

₩ dk

₩R

V∰ s

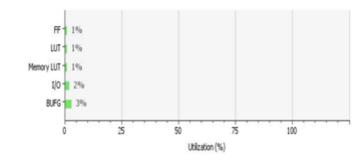

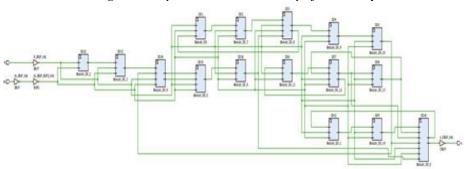

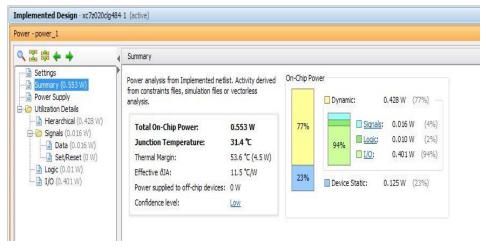

The length of the pseudo-random suit of the circuit is 1023 bits. The electrical circuit of this Kasami pseudo-random sequence generator is presented on Fig.3. The circuit is described in VHDL and then simulated in Vivado 2014. The simulation results are presented on Fig.4 where *s* is the output signal. There the pseudo-ransom bit sequence is generated. In VHDL code D flipflops are with additional Reset entry. Then the Kasami circuit is implemented on XC7Z020CLG484-1 circuit. Fig.5. shows the post-implementation utilization and Fig 6 shows the schematic generated in Vivado. Fig. 7 shows the results from the power analysis of Kasami pseudo-random sequence generator implemented on XC7Z020CLG484-1 circuit. The total on-chip power is 0.553 W. The Junction temperature is 31.4°C and the Thermal margin is 53.6°C (4,5W). The confidence level of this estimation is considered as low. There is a repartition of the dynamic and static on-chip power, as well as reparation of on-chip power for signals, Logic and Intut/Output. The results confirm the predominance of dynamic power which is 77%. The part of power for Input/Output is the most considerable – 94%.

Value

| 20,000 us | 20,002 us | 20,004 us | 20,006 us | 20,008 us | 0 | 0 | 1

**Fig.4.** Timing diagrams of Kasami pseudo-random sequence generator from Fig.3, after simulation in Vivado 2014 of its VHDL description; *s* is the output signal where the pseudorandom sequence is generated

Fig.5. Post-implementation utilization in project summary

Fig.6. Schematic generated in Vivado

**Fig.7.** Summary with results from the power analysis of Kasami pseudo-random sequence generator, implemented on XC7Z020CLG484-1 circuit.

### **4.2.** Estimation of the Power Consumption of a USRP-Based Realisation of a Communication System

The estimation of the power consumption of an USRP-based system can be done from datasheets of the device. Usually these data indicate the maximal power consumption in the aim to inform the user for the safe power supply of the USRP. The estimate in the datasheet is done by taking the worst-case values and in case of full load when all components are running at maximal power.

**Table 1.** Specification of the power consumption of Ettus N2x0 from [8]

| Spec                 | Тур. | Unit |

|----------------------|------|------|

| POWER                |      |      |

| DC Input             | 6    | V    |

| Current Consumption  | 1.3  | А    |

| w/ WBX Daughterboard | 2.3  | А    |

There is one datasheet for N2x0, although USRP N210 (see Table 1) contains a bigger FPGA - Xilinx Spartan 3A DSP - XC3SD3400A FPGA than USRP N200 which contains Xilinx Spartan 3A DSP1800 FPGA. Based on the given values for the voltage and the current, the power can be calculated as:

$$P = U*I[W]$$

(3)

For different daughterboards, power consumption is different: for the daughterboard WBX, the power consumption is 13.8~W and for the daughterboard Basic RX/TX the power consumption is 7.8~W

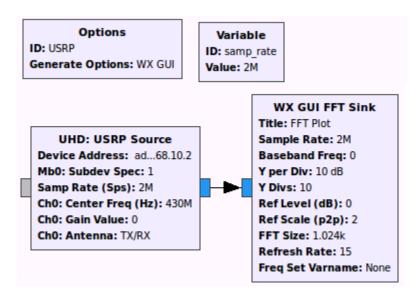

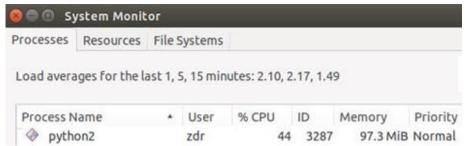

For observing the USRP in GNU Radio [10] a simple flowgraph of a receiver with USRP, which receives the signal and a bloc FFT Sink for visualizing it is designed as shown on Fig.8. The process from the flowgraph in GNU Radio Companion (development of source code in Phyton, describing the flowgraph processing) takes 44 % from the CPU resources. The tool *Gnome System Monitor* [11] gives such information, after being installed and started as an application, as shown on Fig. 9.

**Fig.8.** Flowgraph in GNU Radio of a receiver with USRP, which receives the signal and a bloc FFT Sink for visualizing it

Fig.9. Information given from the tool Gnome System Monitor

**Powerstat -** Power Consumption Calculator for Ubuntu Linux [12] is a specialized tool for calculation of power consumption of components in mobile devices. Once started, it follows the system for about 10 seconds and repeats it again 48 times. The samples collected are for more than 480 seconds. While running, it displays information as: Time – when the monitoring is started, User, Nice – special value, which is priority of processing time for applications, Sys – processor load, Idle - for sleeping mode, Watts - it displays the current power consumption (energy units per second) as shown on Fig. 10.

```

gayan@gayan-Vostro-V131:-$ sudo powerstat -d 2

Running for 470 seconds (47 samples at 10 second intervals).

ACPI battery power measurments will start in 2 seconds time

IRQ/s Fork Exec Exit

Idle

Nice

Sys

IO

Run Ctxt/s

15:01:05

2.1

0.0

2.5

95.3

8.1

3435

2050

0

0

0

18.10

1

15:01:15

0.0

96.9

698

658

0

8

18.38

1.7

1.3

0.1

0

3

93.5

1040

19.34

15:01:25

4.9

0.0

1.6

0.0

1

1289

0

0

0

15:01:35

8.3

0.0

5.3

86.2

0.3

1

9342

5138

1

0

0

19.06

0.0

1069

15:01:45

0.0

0.9

94.0

1286

0

0

19.49

5.1

```

Fig.10. Results generated from Powerstat

After collecting the samples, the calculator gives the values "Average", "Minimum" and "Maximum" for each domain. The summary gives the "Average" percent power consumption together with the standard deviation value for a period of 480 seconds, as shown on Fig.11.

```

Average

0.1

1.6

90.1

0.9

1.6 1670.3 1150.0

20.10

StdDev

5.3

0.3

1.0

6.8

1.0

0.7

930.6

494.9

2.80

0.2

0.0

0.1

81.0

279.4 333.1

Minimum

0.0

1.0

17.01

15.7

3.9

99.6

3.7

3.0 3084.1 1848.8

Maximum

1.5

28.40

Summary:

20.10 Watts on Average with Standard Deviation 2.80

```

Fig.11. Results from the calculator

#### **Conclusion**

The study in this paper shows that recently several methods were proposed for power consumption estimation and reduction at different stages of the communication system design. Providers and developers have answered to the increasing interest of designers to green communications by offering a set of tools and options in CAD systems to allow power consumption estimation. Tools are available in analog, analog/digital and digital design for FPGA implementation. Operational systems as Microsoft and Linux offer free power meter tools which allow determining the power consumption of device components. Two practical examples are given in the paper for power estimation of communication system design on FPGA and USRP platforms. Further research is foreseen on low power optimization of communication system design on both platforms.

**Acknowledgments.** The research described in the paper is partly supported by Project №162PD0020-07 in Technical University – Sofia.

#### References

Nafkha A., Leray P., Louet Y., Palicot J.: Moving a Processing Element from Hot to Cool Spots: Is This an Efficient Method to Decrease Leakage Power Consumption in FPGAs? In: Wu J., Rangan S., Zhang H. (Eds.): Green Communications, Theoretical Fundamentals, Algorithms and Applications, CRC Press, Taylor&Francis Group (2013) 197-215

- 2. Hentati M., Nafkha A., Leray P., Nezan J.-F., Abid M., Software Defined Radio Equipment: What's the Best Design Approach to Reduce Power Consumption and Increase Reconfigurability?, International Journal of Computer Applications (0975 8887), Volume 45–No.14, May (2012) 26-32

- Pandey B., Pattanaik M.: Low Power VLSI Circuit Design with Efficient HDL Coding, Communication Systems and Network Technologies (CSNT), 2013 International Conference on, 6-8 April (2013) 698-705

- Goodman J., Chandrakasan A.P., An Energy-Efficient Reconfigurable Public-Key Cryptography Processor, IEEE journal of solid-state circuits, vol. 36, no. 11, November (2001) 1808-1820

- Zepernick H.-J., Finger A.: Pseudo Random Signal Processing: Theory and Applications, Wiley, 2005

- 6. Cadence ORCAD Design Suit 16.6, Users' guide (2013)

- 7. Analog Filter Wizard, Analog Devices (2016) http://www.analog.com/designtools/en/filterwizard/

- Ettus N200-210 Data Sheet, 14.09.2012, Ettus Research (2012) https://www.ettus.com/content/files/07495\_Ettus\_N200-210\_DS\_Flyer\_HR\_1.pdf

- 9. What is Joulmeter? How does it work?, Microsoft research, December 21 (2011) https://www.microsoft.com/en-us/research/video/joulemeter/

- 10. GNU Radio http://gnuradio.org/

- 11. Gnome System monitor https://help.gnome.org/users/gnome-system-monitor/

- 12. UBUNTO Manuals http://manpages.ubuntu.com/manpages/wily/man8/powerstat.8.html

- Xilinx Power Estimator (XPE) https://www.xilinx.com/products/technology/power/xpe.html

- 14. PowerPlay Early Power Estimators (EPE) and Power Analyzer, https://www.altera.com/support/support-resources/operation-and-testing/power/pow-powerplay.html

- Low power VLSI chip design: Circuit design techniques, EE Harold, http://www.eeherald.com/section/design-guide/Low-Power-VLSI-Design.html

37